[비즈니스포스트] 경계현 삼성전자 DS부문장 겸 대표이사 사장이 반도체 위탁생산(파운드리) 3나노 공정 상용화를 앞두고 수율(결함이 없는 합격품의 비율)을 높이기 위해 온힘을 쏟고 있다.

경 사장은 3나노 공정 상용화 초기단계부터 팹리스(반도체 설계기업)와 협력해 4나노 공정에서 겪었던 수율 저하 문제가 되풀이되지 않도록 하는 데 초점을 맞추고 있는 것으로 보인다.

![삼성전자 첨단파운드리 공정 수율 높인다, 경계현 팹리스와 협력 강화]()

19일 반도체업계에 따르면 경계현 사장이 11일부터 13일까지 반도체 연구소 ‘삼성리서치아메리카’(SRA)를 찾아 연구 현황을 점검하고 파운드리 주요 고객사와 만난 것을 두고 차세대공정인 3나노 파운드리 수주를 위한 행보라는 해석이 나오고 있다.

삼성전자는 올해 상반기부터 3나노 공정 양산에 들어간다는 계획을 세우고 있으며 아직 외부고객사 확보는 이뤄지지 않은 것으로 알려졌다.

일반적으로 파운드리는 삼성전자와 같은 파운드리업체가 자신들의 로드맵에 따라 공정을 공개한 뒤 해당공정이 가지는 특성과 셀 크기를 예시를 들어가며 팹리스에게 설명한다.

이에 팹리스가 위탁생산을 맡기면 파운드리가 테스트 칩을 제조하고 그 뒤 양산하는 과정을 거쳐 팹리스에 약속된 시간에 전달하게 된다.

그런데 사실상 반도체를 설계하는 과정에서부터 팹리스와 파운드리의 협력이 시작된다. 팹리스는 칩을 제작하기 1~2년 전부터 파운드리 제작라인을 감안해 칩을 설계하기 때문이다.

그 뒤 반도체를 생산하는 공정에서도 파운드리와 팹리스의 협업은 지속된다.

파운드리 수율을 끌어올리려면 팹리스 각각의 설계도마다 수많은 미세한 조정이 필요하다. 이러한 조정값은 반도체를 설계한 팹리스가 가장 잘 파악하고 있다.

삼성전자가 4나노 공정으로 퀄컴 모바일프로세서(AP) ‘스냅드래곤8 1세대’를 양산할 때도 퀄컴의 본사 임원과 기술 인력들이 삼성전자 파운드리 공장에 상주하면서 수율을 최대한 높이는 데 도움을 줬던 것으로 알려졌다.

삼성전자의 파운드리 최대 경쟁자인 대만 TSMC가 4나노 수율에서 삼성전자보다 앞설 수 있었던 것은 기술력 차이도 있지만 고객사와 오랜 협업을 통해 노하우를 쌓은 영향이 컸을 것으로 분석되고 있다.

애플과 같은 최대 팹리스가 TSMC에 전적으로 파운드리를 맡기는 것도 업체를 바꿨을 때 감당해야 할 비용과 리스크가 너무 크기 때문이다.

![삼성전자 첨단파운드리 공정 수율 높인다, 경계현 팹리스와 협력 강화]() 따라서 경 사장이 삼성전자 3나노 공정에서 경쟁력을 확보하려면 팹리스와 반도체 설계단계부터 협력을 강화할 필요성이 있다.

따라서 경 사장이 삼성전자 3나노 공정에서 경쟁력을 확보하려면 팹리스와 반도체 설계단계부터 협력을 강화할 필요성이 있다.

이와 관련해 유명 IT 팁스터(정보제공자)인 앤써니는 19일 트위터에 “몇 명의 삼성전자 경영진이 최근 미국으로 출장을 갔고 고객사들과 4나노 및 3나노 공정과 그들이 겪고 있는 문제에 대해 논의했을 것”이라고 말했다.

특히 삼성전자는 3나노부터 새로운 GAA(게이트올어라운드) 공정을 도입하는 만큼 경 사장으로서는 팹리스와 의견을 나눌 요인이 더욱 늘어났다.

반도체 구성 단위인 트랜지스터는 전류가 흐르는 '채널'과 채널을 제어하는 ‘게이트’로 이뤄진다. 게이트올어라운드는 트랜지스터의 채널과 게이트가 4면에서 맞닿게 하는 기술이다.

채널과 게이트 접촉면이 3면에 그치는 기존 ‘핀펫(FinFET)’ 방식보다 반도체가 동작하는 전압을 낮추고 성능을 개선할 수 있다.

시장 조사기관 IC놀리지에 따르면 삼성전자 3나노 공정의 집적도 향상은 1.35배, 같은 전력을 사용할 때 성능 개선폭은 35%, 같은 성능을 활용할 때 전력 감소는 50% 수준에 이르는 것으로 추정됐다. 이는 TSMC의 핀펫 방식 3나노 공정이 성능 개선폭 10%, 전력 감소 25% 정도인 것과 비교해 우월한 것이다.

경 사장은 삼성전자의 반도체 ‘설계자산(IP)’ 확보에도 힘을 쏟고 있는 것으로 전해졌다.

팹리스는 반도체 설계 과정에서 시간을 단축하기 위해 기존에 개발된 설계자산을 활용하는 경우가 많은데 이 설계자산이 파운드리 공정에 최적화돼 있어야 제품 품질이나 수율을 높일 수 있다. 주요 설계자산 업체로는 ARM, 케이던스, 시놉시스 등이 있다.

삼성전자 파운드리사업부는 2020년 기준 7천~1만 개의 설계자산을 보유하고 있는데 이는 TSMC가 보유한 설계자산의 30% 수준에 그친다.

이재윤 유안타증권 연구원은 “단순한 생산능력 확대가 파운드리사업 확대로 이어지지 않는다”며 “파운드리는 서비스업의 성격도 강하기 때문에 우수한 공정 기술력과 충분한 생산능력 외에 설계자산(IP) 라이브러리 및 전후방 인프라가 고객 확보에 결정적인 역할을 한다”고 분석했다. 나병현 기자

경 사장은 3나노 공정 상용화 초기단계부터 팹리스(반도체 설계기업)와 협력해 4나노 공정에서 겪었던 수율 저하 문제가 되풀이되지 않도록 하는 데 초점을 맞추고 있는 것으로 보인다.

▲ 경계현 삼성전자 DS부문장 겸 대표이사 사장.

19일 반도체업계에 따르면 경계현 사장이 11일부터 13일까지 반도체 연구소 ‘삼성리서치아메리카’(SRA)를 찾아 연구 현황을 점검하고 파운드리 주요 고객사와 만난 것을 두고 차세대공정인 3나노 파운드리 수주를 위한 행보라는 해석이 나오고 있다.

삼성전자는 올해 상반기부터 3나노 공정 양산에 들어간다는 계획을 세우고 있으며 아직 외부고객사 확보는 이뤄지지 않은 것으로 알려졌다.

일반적으로 파운드리는 삼성전자와 같은 파운드리업체가 자신들의 로드맵에 따라 공정을 공개한 뒤 해당공정이 가지는 특성과 셀 크기를 예시를 들어가며 팹리스에게 설명한다.

이에 팹리스가 위탁생산을 맡기면 파운드리가 테스트 칩을 제조하고 그 뒤 양산하는 과정을 거쳐 팹리스에 약속된 시간에 전달하게 된다.

그런데 사실상 반도체를 설계하는 과정에서부터 팹리스와 파운드리의 협력이 시작된다. 팹리스는 칩을 제작하기 1~2년 전부터 파운드리 제작라인을 감안해 칩을 설계하기 때문이다.

그 뒤 반도체를 생산하는 공정에서도 파운드리와 팹리스의 협업은 지속된다.

파운드리 수율을 끌어올리려면 팹리스 각각의 설계도마다 수많은 미세한 조정이 필요하다. 이러한 조정값은 반도체를 설계한 팹리스가 가장 잘 파악하고 있다.

삼성전자가 4나노 공정으로 퀄컴 모바일프로세서(AP) ‘스냅드래곤8 1세대’를 양산할 때도 퀄컴의 본사 임원과 기술 인력들이 삼성전자 파운드리 공장에 상주하면서 수율을 최대한 높이는 데 도움을 줬던 것으로 알려졌다.

삼성전자의 파운드리 최대 경쟁자인 대만 TSMC가 4나노 수율에서 삼성전자보다 앞설 수 있었던 것은 기술력 차이도 있지만 고객사와 오랜 협업을 통해 노하우를 쌓은 영향이 컸을 것으로 분석되고 있다.

애플과 같은 최대 팹리스가 TSMC에 전적으로 파운드리를 맡기는 것도 업체를 바꿨을 때 감당해야 할 비용과 리스크가 너무 크기 때문이다.

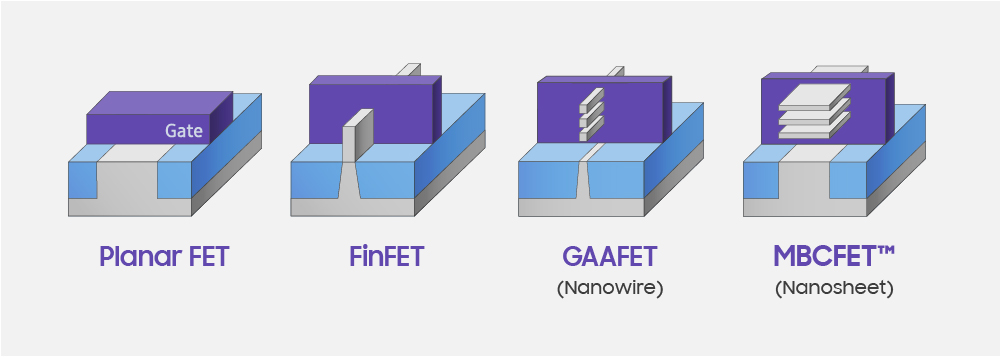

▲ 반도체 트랜지스터 구조. 왼쪽부터 기존 평면 구조, 핀펫, 게이트올어라운드(GAA), 다중가교채널 트랜지스터(MBCFET). <삼성전자>

이와 관련해 유명 IT 팁스터(정보제공자)인 앤써니는 19일 트위터에 “몇 명의 삼성전자 경영진이 최근 미국으로 출장을 갔고 고객사들과 4나노 및 3나노 공정과 그들이 겪고 있는 문제에 대해 논의했을 것”이라고 말했다.

특히 삼성전자는 3나노부터 새로운 GAA(게이트올어라운드) 공정을 도입하는 만큼 경 사장으로서는 팹리스와 의견을 나눌 요인이 더욱 늘어났다.

반도체 구성 단위인 트랜지스터는 전류가 흐르는 '채널'과 채널을 제어하는 ‘게이트’로 이뤄진다. 게이트올어라운드는 트랜지스터의 채널과 게이트가 4면에서 맞닿게 하는 기술이다.

채널과 게이트 접촉면이 3면에 그치는 기존 ‘핀펫(FinFET)’ 방식보다 반도체가 동작하는 전압을 낮추고 성능을 개선할 수 있다.

시장 조사기관 IC놀리지에 따르면 삼성전자 3나노 공정의 집적도 향상은 1.35배, 같은 전력을 사용할 때 성능 개선폭은 35%, 같은 성능을 활용할 때 전력 감소는 50% 수준에 이르는 것으로 추정됐다. 이는 TSMC의 핀펫 방식 3나노 공정이 성능 개선폭 10%, 전력 감소 25% 정도인 것과 비교해 우월한 것이다.

경 사장은 삼성전자의 반도체 ‘설계자산(IP)’ 확보에도 힘을 쏟고 있는 것으로 전해졌다.

팹리스는 반도체 설계 과정에서 시간을 단축하기 위해 기존에 개발된 설계자산을 활용하는 경우가 많은데 이 설계자산이 파운드리 공정에 최적화돼 있어야 제품 품질이나 수율을 높일 수 있다. 주요 설계자산 업체로는 ARM, 케이던스, 시놉시스 등이 있다.

삼성전자 파운드리사업부는 2020년 기준 7천~1만 개의 설계자산을 보유하고 있는데 이는 TSMC가 보유한 설계자산의 30% 수준에 그친다.

이재윤 유안타증권 연구원은 “단순한 생산능력 확대가 파운드리사업 확대로 이어지지 않는다”며 “파운드리는 서비스업의 성격도 강하기 때문에 우수한 공정 기술력과 충분한 생산능력 외에 설계자산(IP) 라이브러리 및 전후방 인프라가 고객 확보에 결정적인 역할을 한다”고 분석했다. 나병현 기자

![[한국갤럽] 이재명 지지율 61%로 3%p 내려, 민주당 45% vs 국힘 23%](https://businesspost.co.kr/news/photo/202605/20260515114313_87595.jpg)