삼성전자가 차세대 반도체 노광장비 기술력을 확보해 경쟁사와 기술격차를 벌릴 것으로 전망된다.

도현우 NH투자증권 연구원은 3일 “삼성전자가 6월26일 투자자포럼을 열고 EUV(극자외선 노광기술)보다 더 미세한 반도체 공정을 가능하게 하는 High NA EUV 등 반도체 공정 신기술을 공개했다”며 “신기술이 반도체 양산에 본격적으로 도입되기 시작하면 공정능력 격차가 확대될 것”이라고 내다봤다.

![삼성전자, 차세대 반도체 공정기술로 경쟁사와 격차 더 벌릴 능력 과시]()

삼성전자는 글로벌 반도체기업 가운데 가장 빠르게 EUV를 반도체 양산에 도입한 기업으로 꼽힌다.

포럼 내용에 따르면 하반기부터 7nm(나노미터) 로직 반도체 공정과 1znm(10나노미터 초반) DRAM 공정에도 EUV를 적용하겠다는 계획을 세웠다.

EUV는 반도체 원재료인 웨이퍼에 회로를 그리는 노광기 가운데 최첨단 장비로 파장의 길이가 14분의 1 미만이어서 공정 수를 줄여 생산성을 높여준다.

도 연구원은 “EUV를 적용한 양산도 본격적으로 하지 않은 상태에서 벌써 High NA EUV를 내놓았다는 점이 이색적”이라며 “EUV 이후 노광장비 관련 논의가 벌써 이루어지는 이유는 EUV의 양산 도입이 4년 정도 너무 늦어졌기 때문에 효용가치가 줄어들고 있어 다음 세대 노광장비를 놓고 조기에 논의할 할 필요성이 커지고 있는 것”이라고 분석했다.

EUV는 4년 전만 해도 효율적 기술이었으나 도입이 늦춰지면서 한계가 빠르게 다가올 가능성이 큰 것으로 분석됐다.

EUV 도입이 지연된 4년 동안 반도체업체들은 기존 노광장비 ArF-I의 기술을 최대한 끌어올려 멀티 패터닝이라는 방법을 개발해 공정 미세화를 지속했다.

현재 EUV 기술력으로는 10nm 이하에서는 EUV를 활용해도 멀티 패터닝이 필요한 것으로 파악된다. 멀티 패터닝은 비용 상승으로 이어진다.

이에 따라 반도체업계는 다른 기술을 찾을 수밖에 없는 상황인데 이번에 삼성전자가 발표한 High NA EUV는 8nm(나노미터) 이하 로직에서도 멀티 패터닝 없이 한 번에 공정이 가능한 것으로 알려졌다.

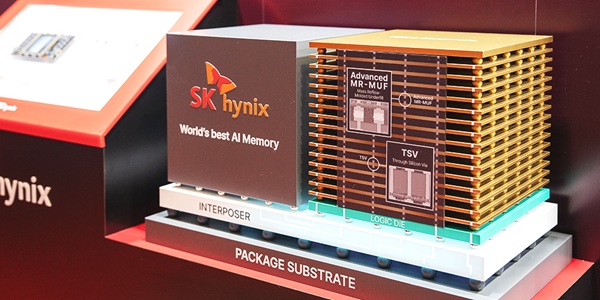

도 연구원은 “삼성전자는 반도체 신기술에 대한 대처능력을 글로벌 최고 수준임을 보여주고 있다”며 “차세대 메모리시장이 조성될 때는 언제든 시장 장악이 가능하도록 기술 개발을 진행하고 있다”고 파악했다. [비즈니스포스트 조예리 기자]

도현우 NH투자증권 연구원은 3일 “삼성전자가 6월26일 투자자포럼을 열고 EUV(극자외선 노광기술)보다 더 미세한 반도체 공정을 가능하게 하는 High NA EUV 등 반도체 공정 신기술을 공개했다”며 “신기술이 반도체 양산에 본격적으로 도입되기 시작하면 공정능력 격차가 확대될 것”이라고 내다봤다.

▲ 김기남 삼성전자 DS부문 대표이사 부회장.

삼성전자는 글로벌 반도체기업 가운데 가장 빠르게 EUV를 반도체 양산에 도입한 기업으로 꼽힌다.

포럼 내용에 따르면 하반기부터 7nm(나노미터) 로직 반도체 공정과 1znm(10나노미터 초반) DRAM 공정에도 EUV를 적용하겠다는 계획을 세웠다.

EUV는 반도체 원재료인 웨이퍼에 회로를 그리는 노광기 가운데 최첨단 장비로 파장의 길이가 14분의 1 미만이어서 공정 수를 줄여 생산성을 높여준다.

도 연구원은 “EUV를 적용한 양산도 본격적으로 하지 않은 상태에서 벌써 High NA EUV를 내놓았다는 점이 이색적”이라며 “EUV 이후 노광장비 관련 논의가 벌써 이루어지는 이유는 EUV의 양산 도입이 4년 정도 너무 늦어졌기 때문에 효용가치가 줄어들고 있어 다음 세대 노광장비를 놓고 조기에 논의할 할 필요성이 커지고 있는 것”이라고 분석했다.

EUV는 4년 전만 해도 효율적 기술이었으나 도입이 늦춰지면서 한계가 빠르게 다가올 가능성이 큰 것으로 분석됐다.

EUV 도입이 지연된 4년 동안 반도체업체들은 기존 노광장비 ArF-I의 기술을 최대한 끌어올려 멀티 패터닝이라는 방법을 개발해 공정 미세화를 지속했다.

현재 EUV 기술력으로는 10nm 이하에서는 EUV를 활용해도 멀티 패터닝이 필요한 것으로 파악된다. 멀티 패터닝은 비용 상승으로 이어진다.

이에 따라 반도체업계는 다른 기술을 찾을 수밖에 없는 상황인데 이번에 삼성전자가 발표한 High NA EUV는 8nm(나노미터) 이하 로직에서도 멀티 패터닝 없이 한 번에 공정이 가능한 것으로 알려졌다.

도 연구원은 “삼성전자는 반도체 신기술에 대한 대처능력을 글로벌 최고 수준임을 보여주고 있다”며 “차세대 메모리시장이 조성될 때는 언제든 시장 장악이 가능하도록 기술 개발을 진행하고 있다”고 파악했다. [비즈니스포스트 조예리 기자]

![[한국갤럽] 이재명 지지율 61%로 3%p 내려, 민주당 45% vs 국힘 23%](https://businesspost.co.kr/news/photo/202605/20260515114313_87595.jpg)