![삼성전자 3나노는 자체 반도체에 적용 예상, 파운드리는 4나노 전망]()

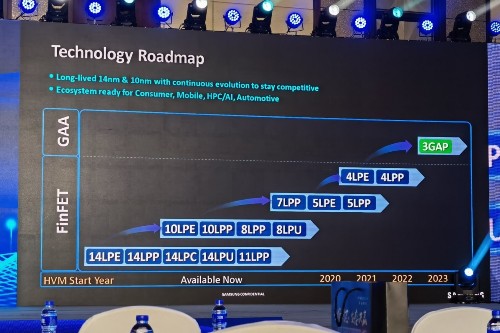

| ▲ 삼성전자 파운드리 공정 로드맵. 2022년 2세다 4나노급 공정(4LPP), 2023년 2세대 3나노급 공정(3GA) 양산이 예정됐다. <웨이보 계정 과기심시공(@科技芯时空) 갈무리> |

삼성전자가 파운드리(반도체 위탁생산)시장의 공략을 위해 최첨단 반도체 공정을 단계별로 다른 전략을 구사할 것으로 보인다.

가장 발전된 3나노급 공정은 일감이 많은 자체설계 반도체에 먼저 적용하고, 상대적으로 고객사에 친숙한 4나노급 공정은 외부 반도체 일감에 적용할 것으로 전망된다.

11일 반도체업계에 따르면 삼성전자는 최근 중국 상하이에서 열린 ‘국내 설계자산 및 맞춤형 반도체 생태계 콘퍼런스’에 참석해 최신 파운드리 로드맵을 공개했다.

삼성전자의 로드맵를 보면 2세대 3나노급 공정(GAP)이 2023년 양산(HVM)에 들어간다. 다만 이보다 초기 공정인 1세대 3나노급 공정(GAE)의 양산시기는 표시되지 않았다.

삼성전자는 2022년부터 3나노급 공정 기반의 반도체 양산을 시작할 것으로 알려졌다. 반도체설계자동화업체 시놉시스는 6월 삼성전자의 3나노급 공정을 이용한 반도체 테이프아웃에 성공했다고 밝히기도 했다. 반도체 설계를 마쳐 생산단계에 들어갈 수 있게 됐다는 뜻이다.

1세대 3나노급 공정 양산을 준비하는 삼성전자가 이처럼 로드맵을 따로 내놓지 않은 이유를 두고 외국 언론에서는 외부 고객사의 비중이 적기 때문이라고 추정이 나왔다.

1세대 3나노급 공정이 삼성전자 내부에서 설계하는 자체 반도체를 중심으로 적용될 가능성이 높다는 것이다.

기술매체 아난드테크는 “공개 로드맵에 1세대 3나노급 공정이 없는 것은 다른 초기 공정과 마찬가지로 삼성전자 시스템LSI사업부에서만 사용한다는 뜻일 수 있다”며 “일반 고객은 2023년까지 삼성의 3나노급 공정을 사용하지 않을 것으로 보인다”고 말했다.

삼성전자 시스템LSI사업부는 스마트폰용 애플리케이션 프로세서(AP) 엑시노스 시리즈 등 고성능 반도체에 파운드리사업부의 최신 공정을 적용해 개발하고 있다. 올해 초 출시된 엑시노스2100의 경우 삼성전자 파운드리사업부 5나노급 공정에서 생산된다.

파운드리사업부의 전체 매출비중을 봐도 시스템LSI사업부의 일감이 50%를 웃도는 것으로 파악된다. 초기 3나노급 공정의 수요가 삼성전자 자체 반도체에 쏠릴 것으로 예상되는 이유다.

이에 따라 삼성전자 파운드리사업부는 내년 주력 공정으로 1세대 3나노급 공정 대신 2세대 4나노급 공정(4LPP)을 내세울 것으로 전망된다.

![삼성전자 3나노는 자체 반도체에 적용 예상, 파운드리는 4나노 전망]()

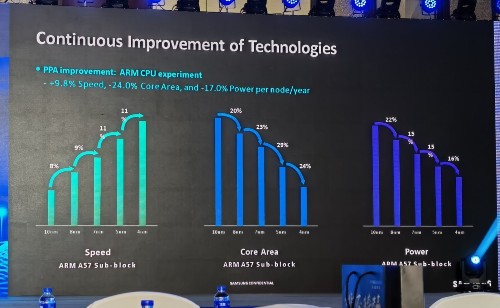

| ▲ 삼성전자 파운드리 공정별 성능 개선폭. <웨이보 계정 과기심시공(@科技芯时空) 갈무리> |

이번에 공개된 삼성전자의 로드맵에 따르면 올해 하반기 1세대 4나노급 공정 양산을 시작하고 내년에는 2세대 4나노급 공정 양산이 추진된다.

2세대 4나노급 공정이 적용된 반도체는 5나노급 반도체와 비교해 성능 11% 개선, 칩 면적 24% 축소, 전력 사용량 16% 절감 등의 효과를 보이는 것으로 전해졌다.

물론 이는 3나노급 반도체의 성능 개선폭보다는 낮은 수준이다.

삼성전자 3나노급 공정은 5나노급 공정과 비교해 성능 30% 개선, 전력 효율 50% 향상, 칩 면적 35% 절감 등을 달성할 수 있는 것으로 알려졌다.

다만 현재 7나노급 이하 공정을 제공하는 파운드리기업이 삼성전자와 대만 TSMC밖에 없다는 점을 놓고 보면 삼성전자의 2세대 4나노급 공정에 관해서도 시장 수요가 충분할 것으로 예상된다.

기존 기술인 ‘핀펫’을 활용해 고객사의 접근이 더 쉽다는 것도 4나노급 공정의 이점으로 꼽힌다.

아난드테크는 “2세대 4나노급 공정은 핀펫 구조에 의존한다”며 “삼성 고객들이 초기 3나노급 공정보다 2세대 4나노급 공정을 이용하는 것이 훨씬 수월할 것이다”고 말했다.

반도체는 공정 수준이 고도화할수록 설계비용이 기하급수적으로 늘어난다. 시장 조사업체 IBS에 따르면 공정별 반도체 설계비용은 7나노급 2억2230만 달러, 5나노급 4억1600만 달러, 3나노급 5억9천만 달러 등으로 증가한다.

반도체 설계 전문기업(팹리스)들이 삼성전자 3나노급 공정 기반 반도체를 설계할 때는 특히 더 많은 시간과 비용이 소요될 공산이 크다. 삼성전자 3나노급 공정은 핀펫을 적용했던 이전 공정과 달리 새로운 트랜지스터 구조인 게이트올어라운드(GAA)를 채택했기 때문이다.

반도체 전문매체 세미콘덕터엔지니어링은 IBS를 인용해 “게이트올어라운드 기반 3나노급 반도체의 설계비용은 핀펫 기반 3나노급 반도체와 크게 다르지 않아야 한다”며 “다만 게이트올어라운드 공정을 위한 반도체 설계자산 사용 비용이 핀펫 공정의 1.5배에 이른다는 것이 과제다”고 보도했다.

세계 1위 파운드리기업 TSMC는 삼성전자와 다르게 3나노급 공정에서 기존 트랜지스터 구조 핀펫을 그대로 유지하는 것으로 알려졌다. 또 2022년 3나노급 공정 양산을 시작할 것으로 전해졌다.

삼성전자는 TSMC와 격차를 좁히기 위해 3나노급 공정뿐 아니라 4나노급 공정의 확대에도 힘을 기울일 것으로 보인다.

시장 조사업체 트렌드포스에 따르면 1분기 파운드리시장 점유율은 TSMC 56%, 삼성전자 18% 등으로 추산됐다. 삼성전자 점유율은 외부 고객사와 시스템LSI사업부의 반도체 일감을 모두 합쳐 집계됐다. [비즈니스포스트 임한솔 기자]