!["TSMC 2나노 반도체 수율 3나노 추월", 삼성전자 인텔 추격 계속 따돌려]()

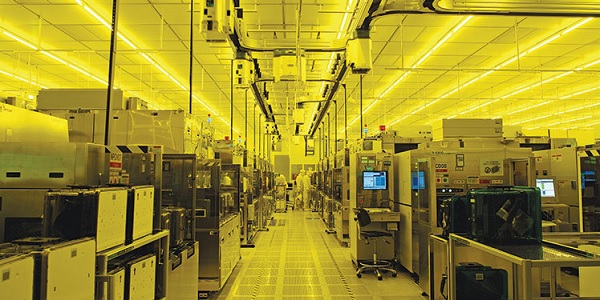

| ▲ TSMC 2나노 파운드리 수율이 3나노 반도체 양산을 시작하기 직전과 비교해 높은 수준까지 올라왔다는 대만언론 보도가 나왔다. 이는 삼성전자 및 인텔과 경쟁에 유리한 요소로 지목된다. TSMC 반도체 생산공장 내부 사진. |

[비즈니스포스트] TSMC가 하반기 양산을 앞둔 2나노 미세공정 파운드리 수율이 이미 3나노 반도체 생산 직전보다 높은 수준을 기록했다는 외신 보도가 나왔다.

7일 대만 공상시보 보도에 따르면 TSMC 2나노 공정은 이미 애플과 엔비디아, AMD와 퀄컴, 브로드컴과 미디어텍 등 다수의 대형 고객사를 확보한 것으로 파악된다.

이들은 모두 TSMC의 3나노 미세공정 파운드리를 활용했는데 차기 제품에 적용되는 반도체 생산 기술에도 굳건한 신뢰를 보이고 있는 셈이다.

공상시보는 하반기 양산을 준비중인 2나노 반도체 웨이퍼의 면적당 평균 결함 수가 이미 5나노와 유사한 수준까지 올라왔고 3나노 생산 직전 단계보다 높아졌다고 보도했다.

웨이퍼 면적당 평균 결함 수는 파운드리 수율을 측정하는 기준 가운데 하나다. 이는 생산성과 원가 경쟁력에 중요한 요소로 꼽힌다.

2나노 수율이 이전에 큰 성공을 거뒀던 3나노 파운드리 초기 단계보다 높아졌다는 것은 TSMC 실적에 기여하는 효과도 더 빠르게 가시화될 수 있다는 의미로 해석된다.

공상시보는 애플 아이폰18 시리즈용 프로세서와 AMD의 차기 서버용 CPU, 엔비디아 ‘루빈’ 시리즈 인공지능 반도체와 인텔 고사양 프로세서가 모두 TSMC 2나노를 활용할 것이라고 전했다.

웨이저자 TSMC CEO도 2나노 파운드리에 주요 고객사 수요가 전례 없는 수준이라는 점을 공식 석상에서 여러 차례 언급하며 강한 자신감을 보이고 있다.

TSMC의 2나노 파운드리 수율 향상은 게이트올어라운드(GAA) 기술을 처음 적용하는 공정이라는 점에서 더욱 주목할 만한 성과로 평가받는다.

경쟁사인 삼성전자는 이미 3나노 공정부터 반도체 성능 및 전력효율을 높일 수 있는 GAA 기술을 활용했는데 이는 수율 부진의 원인 가운데 하나로 추정되기 때문이다.

TSMC는 올해 4분기까지 대만 신주 공장에서 2나노 반도체 웨이퍼(반도체 원판) 기준 월 3만 장, 내년 1분기까지 가오슝 공장에서도 월 3만 장의 생산 능력을 갖추겠다는 목표를 두고 있다.

2027년이면 두 공장의 2나노 반도체 생산량은 월 12만~13만 장 수준에 이를 것으로 예상된다. 2028년에는 미국 애리조나 공장에도 2나노 미세공정이 도입된다.

TSMC가 2나노 파운드리 수율 향상에 힘입어 생산 능력을 공격적으로 확대하는 것은 삼성전자 및 인텔과 경쟁에서 강력한 우위를 확보하는 데 기여할 공산이 크다.

삼성전자는 TSMC와 2나노 파운드리 수주 경쟁에서 승기를 잡기 위해 하반기로 계획하고 있던 양산 시점을 2분기로 앞당기겠다는 계획을 최근 콘퍼런스콜에서 밝혔다.

인텔도 하반기부터 TSMC 2나노 공정과 경쟁할 수 있는 18A(1.8나노급) 파운드리 기술을 상용화해 고객사 반도체 위탁생산에 활용한다는 계획을 두고 있다.

그러나 두 경쟁사 모두 반도체 수율을 비롯한 실제 양산성 및 기술력 측면에서 다소 약점을 안고 있다.

TSMC가 이미 2나노 파운드리 수율을 대폭 끌어올린데다 다수의 대형 고객사 위탁생산 주문도 선점한 만큼 경쟁사들의 추격이 쉽지 않을 것이라는 전망이 나온다.

공상시보는 “TSMC의 2나노 수율 향상은 하반기 양산을 앞두고 자신감을 키울 수 있도록 했다”며 관련 기업에도 수혜가 퍼질 것이라는 관측을 전했다. 김용원 기자